# MỤC LỤC

# **Protected by PDF Anti-Copy Free**

| Muc luc(Upgrade to Pro Version to Remove the Watermark)     | I  |

|-------------------------------------------------------------|----|

| Lời nói đâu                                                 | V  |

| Các từ viết tắt                                             | VI |

| Chương 1: GIỚI THIỆU CHUN PDF IẾN TRÚC MÁY TÍNH             | 1  |

| 1.1. CÁC KHÁI NIỆM VÀ NGUY CƠ BẢN                           | 1  |

| 1.1.1. Mở đầu                                               | 1  |

| 1.1.2. Khái niệm máy tính                                   | 1  |

| 1.1.3. Kiến trúc máy tính và cấu trúc máy tính              |    |

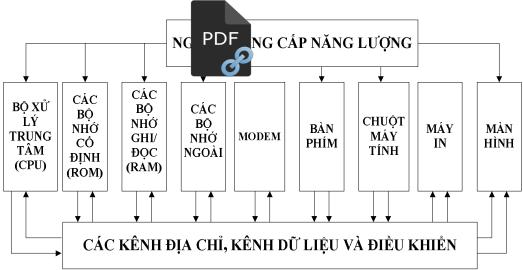

| 1.2. CÁC THÀNH PHẦN CƠ BẢN CỦA MÁY TÍNH                     | 3  |

| 1.2.1. Bộ nguồn                                             | 3  |

| 1.2.1.1. Nguồn cấp điện cho máy lớn                         | 3  |

| 1.2.1.2. Nguồn pin cho máy tính xách tay                    | 4  |

| 1.2.2. Bản mạch chính                                       | 2  |

| 1.2.2.1. Bộ xử lý trung tâm (CPU – Central Processing Unit) | 4  |

| 1.2.2.2. Bộ nhớ cố định (ROM – Read Only Memory)            | 5  |

| 1.2.2.3. Bộ nhớ ghi/đọc (RAM – Random Access Memory)        | 5  |

| 1.2.2.4. Các bộ nhớ ngoài                                   | 5  |

| 1.2.3. Các thiết bị ngoại vi                                |    |

| 1.2.3.1. Bàn phím (Keyboard)                                |    |

| 1.2.3.2. Màn hình (Monitor)                                 |    |

| 1.2.3.3. Máy in (Printer)                                   |    |

| 1.2.3.4. Modem và các thiết bị ngoại vi khác                |    |

| 1.3. PHẦN MỀM MÁY TÍNH                                      |    |

| 1.4. LỊCH SỬ PHÁT TRIỂN MÁY TÍNH                            |    |

| 1.5. KIẾN TRÚC MÁY TÍNH VON-NEUMANN                         |    |

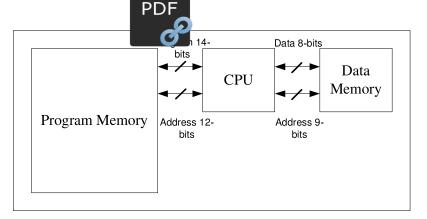

| 1.6. KIẾN TRÚC MÁY TÍNH HAVARD                              |    |

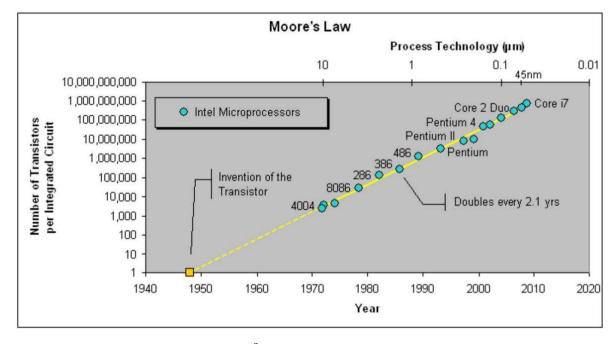

| 1.7. ĐỊNH LUẬT MOORE                                        |    |

| Chương 2: BIỂU DIỄN THÔNG TIN TRONG MÁY TÍNH                |    |

| 2.1. HỆ ĐÊM                                                 |    |

| 2.1.1. Hệ thập phân                                         |    |

| 2.1.2. Hệ nhị phân                                          |    |

| 2.1.2.1. Khái niệm                                          |    |

| 2.1.2.2. Biến đổi từ nhị phân sang thập phân                |    |

| 2.1.2.3. Biến đối thập phân sang nhị phân                   |    |

| 2.1.3. Hệ thập lục phân                                     |    |

| 2.1.3.1. Khái niệm                                          |    |

| 2.1.3.2. Biến đổi thập lục phân sang thập phân              |    |

| 2.1.3.3. Biến đổi thập phân sang thập lục phân              |    |

| 2.1.3.4. Biến đổi thập lục phân sang nhị phân               | 18 |

| 2.1.3.5. Biến đổi nhị phân sang thập lục phân                                         | 19 |

|---------------------------------------------------------------------------------------|----|

|                                                                                       |    |

| 2.2. BIỂU DIỄN ĐỮ LIỆU SỐ TRONG MÁY TÍNH<br>2.2.1. Nguyên tắc chung về mã hóa dữ liệu | 20 |

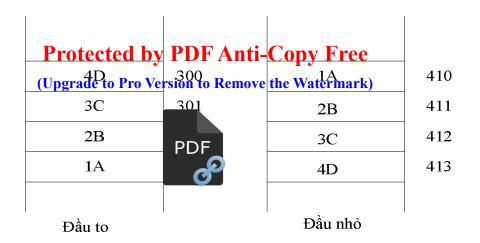

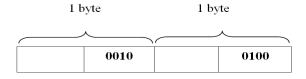

| 2.2.2. Thứ tự ling rade to Broe Versian to Remove the Watermark)                      | 20 |

| 2.2.3. Biểu diễn số nguyên                                                            | 21 |

| 2.2.3.1. Biểu diễn số nguyên                                                          | 21 |

| 2.2.3.2. Biểu diễn số nguyên PDF                                                      | 22 |

| 2.2.3.2. Biểu diễn số nguyên 2.2.4. Các phép toán số học với                          | 23 |

| 2.2.5. Biểu diễn số thực                                                              | 25 |

| 2.2.6. Biểu diễn ký tự                                                                | 28 |

| 2.2.6.1. Bộ mã ASCII                                                                  | 28 |

| 2.2.6.2. Bộ mã Unicode                                                                | 30 |

| 2.2.6.3. Mã BCD (Binary Coded Decimal)                                                | 30 |

| Chương 3: BỘ XỬ LÝ TRUNG TÂM CPU                                                      | 33 |

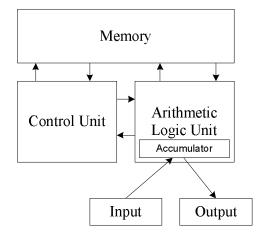

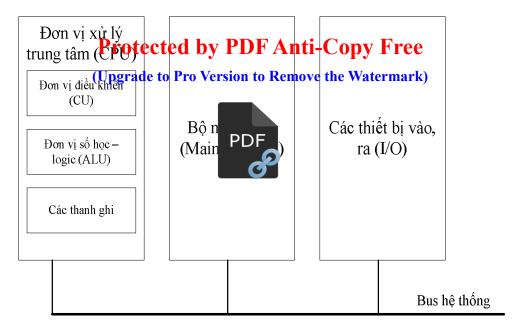

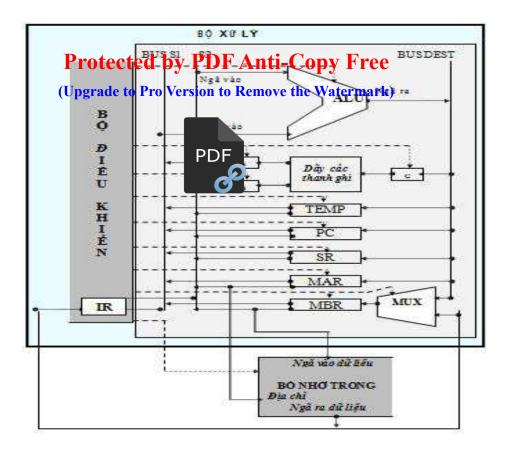

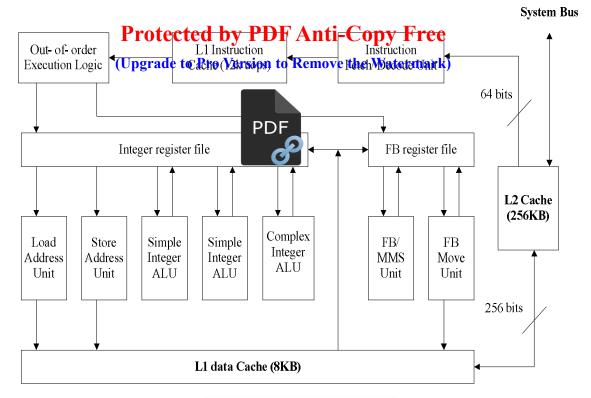

| 3.1. CÂU TRÚC, CHỨC NĂNG CỦA BỘ VI XỬ LÝ                                              | 33 |

| 3.1.1. Chức năng của bộ vi xử lý                                                      | 33 |

| 3.1.2. Cấu trúc của bộ vi xử lý                                                       | 33 |

| 3.2. CÁC THANH GHI                                                                    | 34 |

| 3.2.1. Các thanh ghi đa năng (general registers)                                      | 34 |

| 3.2.2. Các thanh ghi đoạn (segment registers)                                         | 35 |

| 3.2.3. Các thanh ghi con trỏ và chỉ số                                                | 36 |

| 3.2.4. Thanh ghi cờ FR (flag register)                                                | 37 |

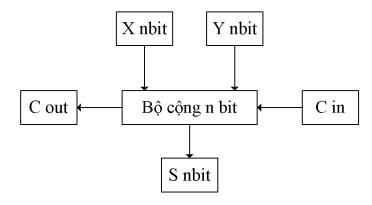

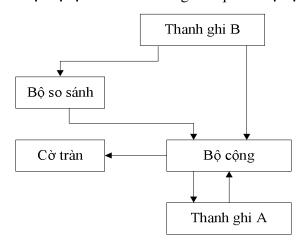

| 3.3. ĐƠN VỊ SỐ HỌC VÀ LOGIC                                                           | 37 |

| 3.3.1. Các phép toán cộng trừ                                                         | 39 |

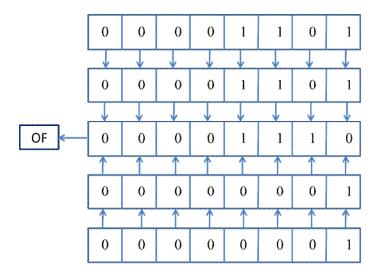

| 3.3.1.1. Phép toán cộng                                                               | 39 |

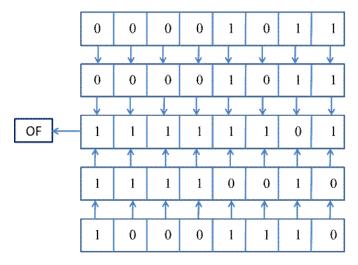

| 3.3.1.2. Phép toán trừ                                                                | 40 |

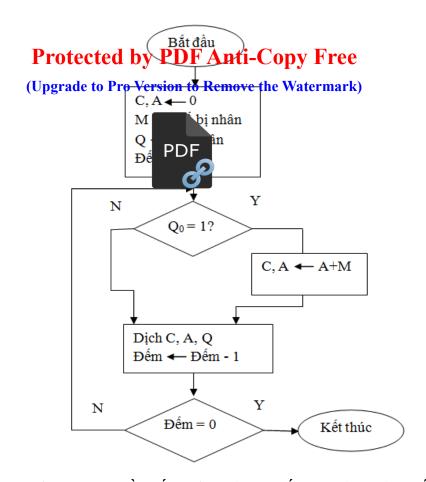

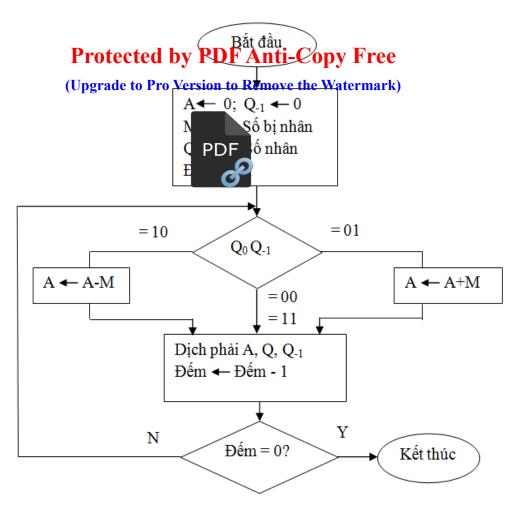

| 3.3.2. Phép nhân số nguyên không dấu                                                  | 41 |

| 3.3.3. Phép nhân số nguyên có dấu                                                     | 42 |

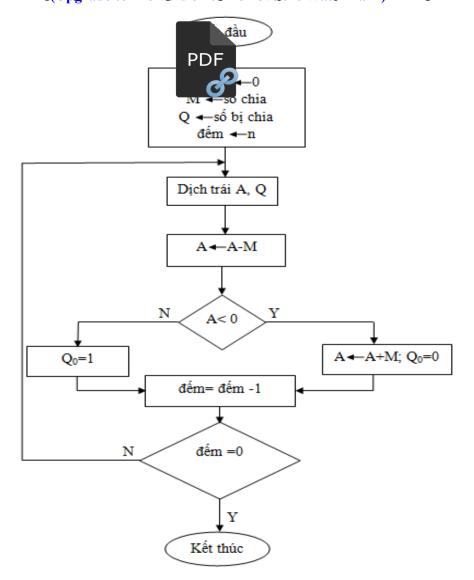

| 3.3.4. Phép chia số nguyên không dấu                                                  | 49 |

| 3.3.5. Phép chia số nguyên có dấu                                                     | 52 |

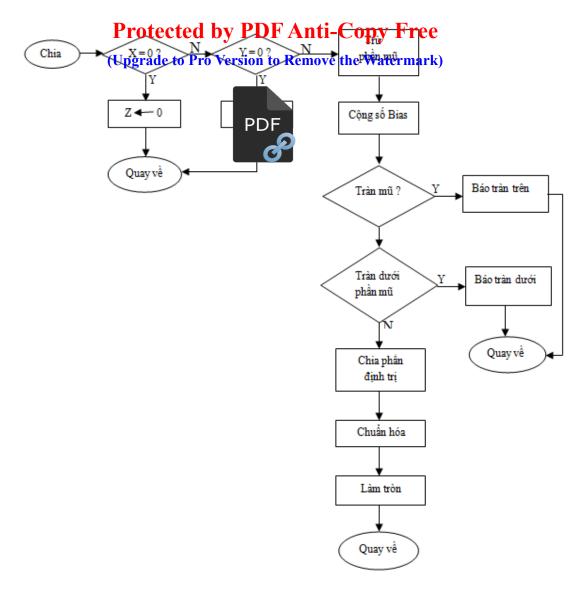

| 3.3.6. Phép toán với số dấu phẩy động                                                 | 54 |

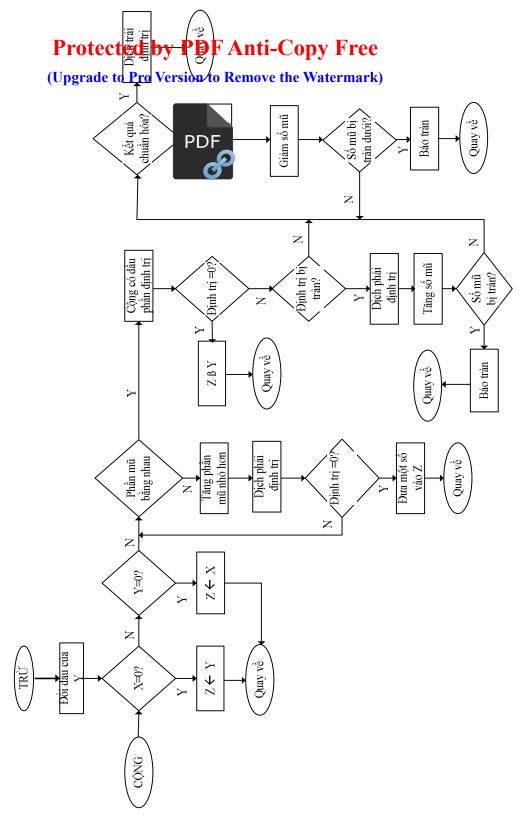

| 3.3.6.1. Phép cộng và trừ                                                             | 54 |

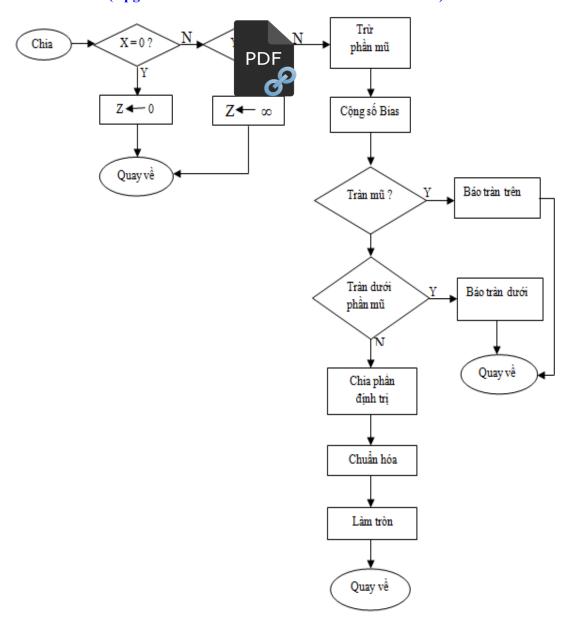

| 3.3.6.2. Phép nhân và chia                                                            | 59 |

| 3.3.6.3. Phép làm tròn                                                                | 61 |

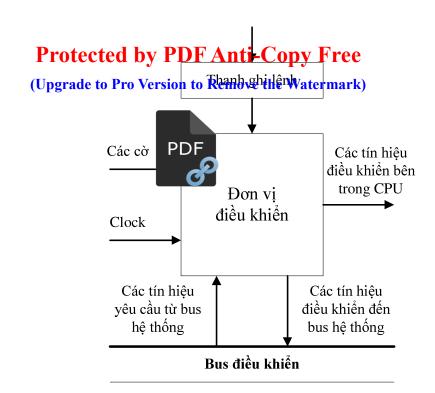

| 3.4. ĐƠN VỊ ĐIỀU KHIỂN                                                                | 63 |

| 3.4.1. TÍn hiệu điều khiển                                                            | 63 |

| 3.4.1.1. Các tín hiệu vào                                                             | 64 |

| 3.4.1.2. Các tín hiệu ra                                                              | 64 |

| 3.4.2. Đơn vị điều khiển vi chương trình                                              | 65 |

| Chương 4: KIẾN TRÚC TẬP LỆNH                                                          |    |

| 4.1. CÁC ĐẶC TRUNG CƠ BẢN CỦA LỆNH MÁY                                                | 67 |

| 4.1.1. Giới thiệu chung về tập lệnh                                                   | 67 |

| 4.1.2. Các thành phần của lệnh máy                                                                                                         | 68  |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.1.3. Mô tả lệnh<br>4.1.4. Các kiểu lệnh                                                                                                  | 68  |

| 4.1.4. Các kiểu lệnh                                                                                                                       | 68  |

| 4.1.5. Các thao tác khi thực hyện lệnh to Remove the Watermark)                                                                            | 69  |

| 4.1.6. Các vấn đề về thiết kế tập lânh                                                                                                     | 69  |

| 4.2. CÁC KIỂU TOÁN HẠNG                                                                                                                    | 69  |

| 4.2.1. Số lượng địa chỉ toán hạn PDF nh                                                                                                    | 70  |

| 4.1.6. Các vấn đề về thiết kế tập lầnh<br>4.2. CÁC KIỀU TOÁN HẠNG<br>4.2.1. Số lượng địa chỉ toán hạn<br>4.2.2. Đánh giá về số địa chỉ toá | 74  |

| 4.3. TẬP LỆNH                                                                                                                              | 74  |

| 4.3.1. Các lệnh chuyển dữ liệu                                                                                                             | 74  |

| 4.3.2. Các lệnh số học                                                                                                                     | 75  |

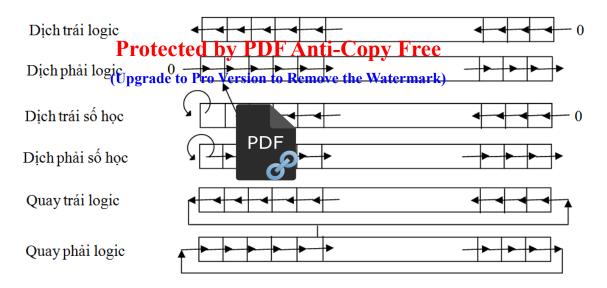

| 4.3.3. Các lệnh logic                                                                                                                      | 75  |

| 4.3.4. Các lệnh vào ra chuyên dụng                                                                                                         |     |

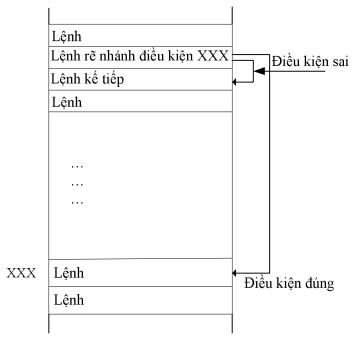

| 4.3.5. Các lệnh chuyển điều kiện                                                                                                           | 76  |

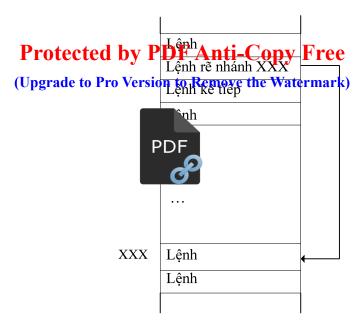

| 4.3.6. Lệnh rẽ nhánh                                                                                                                       | 76  |

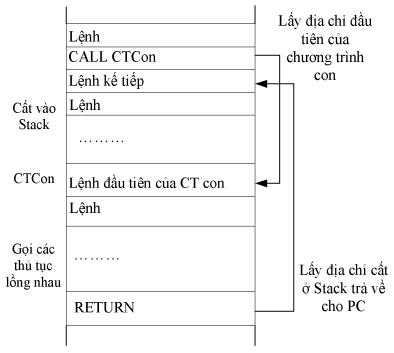

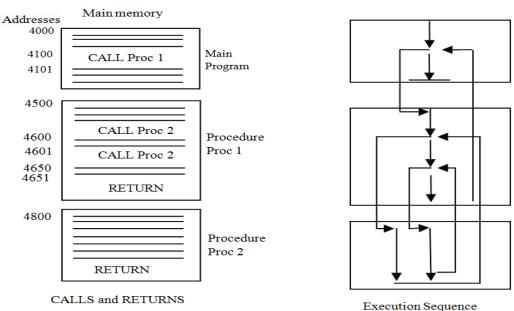

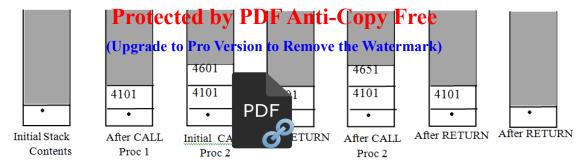

| 4.3.7. Lệnh CALL và RETURN                                                                                                                 | 78  |

| 4.3.8. Các lệnh điều khiển hệ thống                                                                                                        |     |

| 4.4. NGÔN NGỮ LẬP TRÌNH VÀ CHƯƠNG TRÌNH DỊCH                                                                                               | 79  |

| 4.4.1. Khái niệm ngôn ngữ lập trình                                                                                                        | 79  |

| 4.4.2. Các loại ngôn ngữ lập trình thông dụng                                                                                              | 79  |

| 4.4.3. Chương trình dịch                                                                                                                   |     |

| Chương 5: HỆ THỐNG NHÓ                                                                                                                     |     |

| 5.1. TỔNG QUAN VỀ HỆ THỐNG NHỚ                                                                                                             | 83  |

| 5.1.1. Phân loại hệ thống nhớ                                                                                                              | 83  |

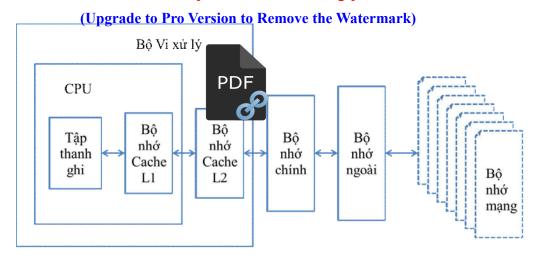

| 5.1.2. Phân cấp hệ thống nhớ                                                                                                               | 85  |

| 5.2. BỘ NHỚ BÁN DẪN                                                                                                                        | 85  |

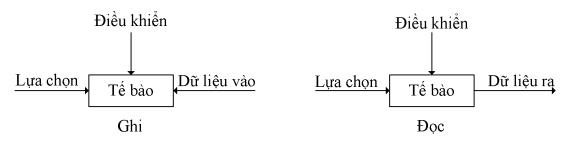

| 5.2.1. Phân loại bộ nhớ bán dẫn                                                                                                            | 85  |

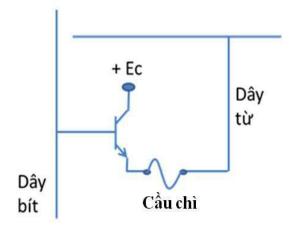

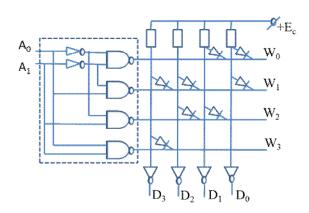

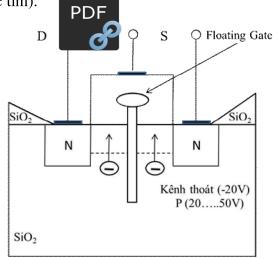

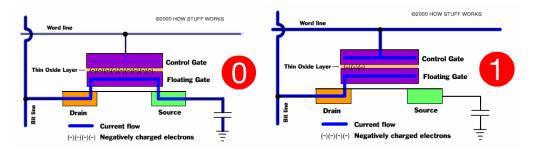

| 5.2.1.1. ROM (Read Only Memory)                                                                                                            | 86  |

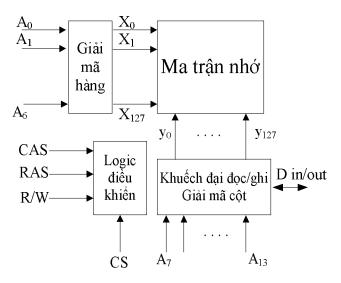

| 5.2.1.2. RAM (Random Access Memory)                                                                                                        | 88  |

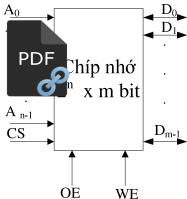

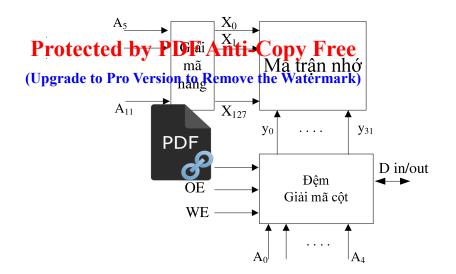

| 5.2.2. Tổ chức của chip nhớ                                                                                                                |     |

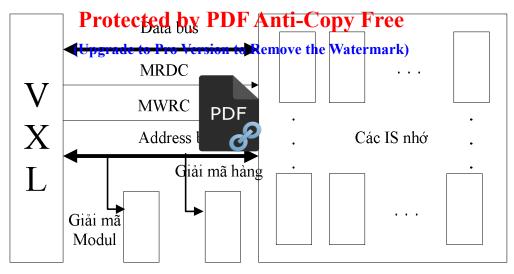

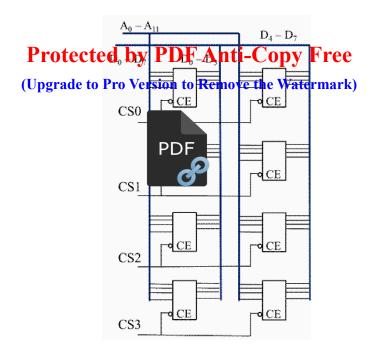

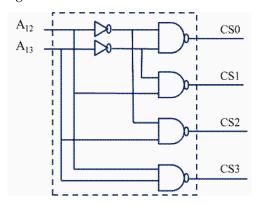

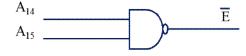

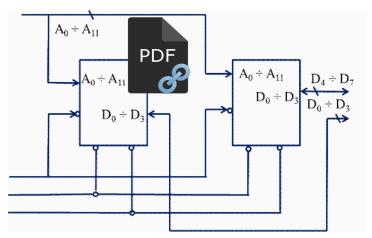

| 5.2.3. Thiết kế mô-đun nhớ bán dẫn                                                                                                         | 91  |

| 5.3. BỘ NHỚ CACHE, BỘ NHỚ TRUY CẬP NHANH                                                                                                   | 96  |

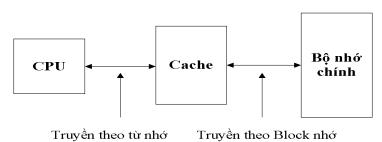

| 5.3.1. Nguyên tắc chung của cache                                                                                                          | 96  |

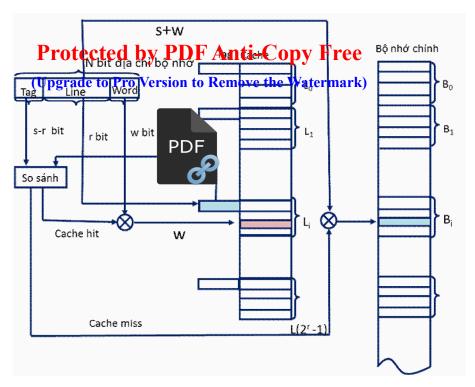

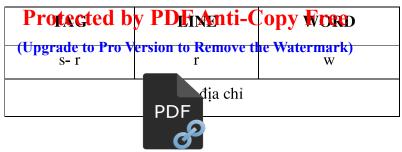

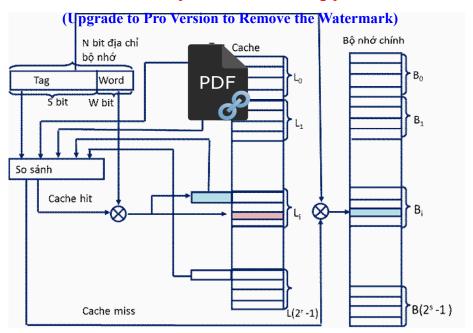

| 5.3.2. Các phương pháp ánh xạ                                                                                                              | 98  |

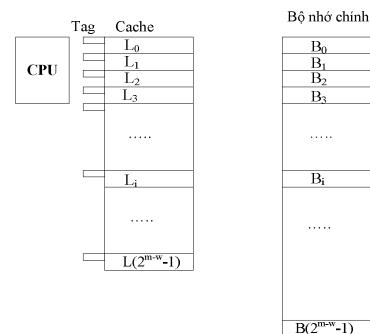

| 5.3.2.1. Ánh xạ trực tiếp (Direct mapping)                                                                                                 | 98  |

| 5.3.2.2. Ánh xạ liên kết toàn phần (Fully associative mapping)                                                                             | 102 |

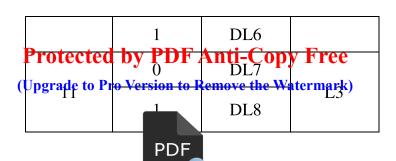

| 5.3.2.3. Ánh xạ liên kết tập hợp                                                                                                           | 105 |

| 5.3.3. Thuật giải thay thế                                                                                                                 | 107 |

| 5.3.4. Phương pháp ghi dữ liệu cache hit                                                                                                   |     |

| 5.3.5. Cache trên các bộ xử lý Intel                                                                                                       |     |

| 5.4. BỘ NHỚ NGOÀI                                                                                                                          | 109 |

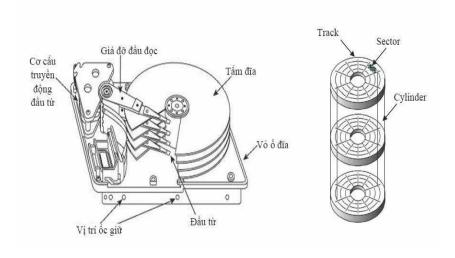

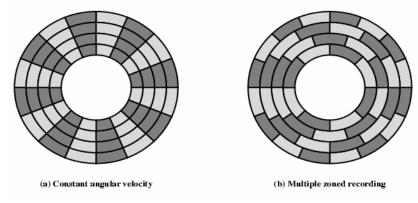

| 5.4.1. Đĩa từ                                                                                                                              | 109 |

| 5.4.2. Đĩa quang                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.4.3. Các loại thể nhất sự thự DDE A thiết Construction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 113 |

| 5.4.3. Các loapthể nhớted by PDF Anti-Copy Free 5.4.4. Băng từ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 113 |

| 5.4.5. Biện phápean do an Bronger sint thu Retroyon thein Vater grant dù                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 114 |

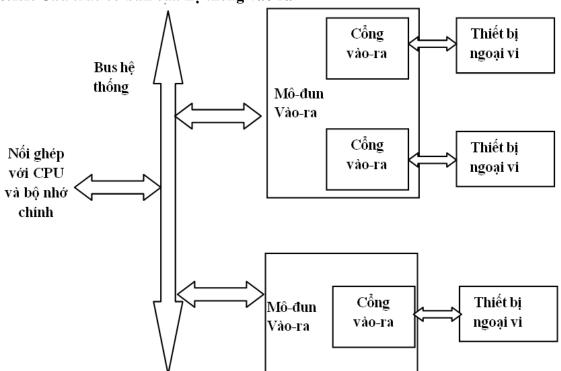

| Chương 6: HỆ THỐNG VÀO RAMONIA (MICHAELLA (M | 116 |

| Chương 6: HỆ THỐNG VÀO RAMING VÀO RAMING VÀO RAMING CỦA HONG CỦA HONG CỦA HONG CỦA HONG VÀO RAMING VÀ RAMING VÀO RAMING VÀO RAMING VÀO RAMING VÀO RAMING VÀO RAMING VÀ RAMING VÀO RAMING VÀO RAMING VÀO RAMING VÀO RAMING VÀO RAMING VÀ RAMING VÀO RAMING VÀ RAMING VÀO RAMING VÀO RAMING VÀO RAMING VÀ RAMI | 116 |

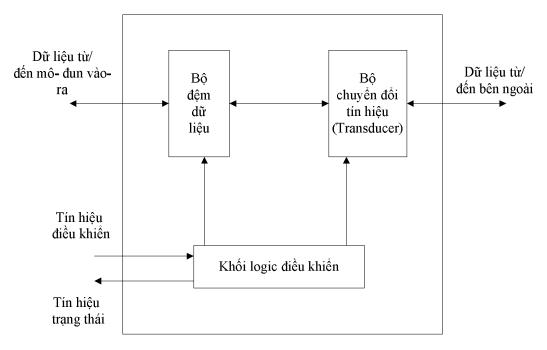

| 6.1.2. Các thiết bị ngoại vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 116 |

| 6.1.2. Các thiết bị ngoại vi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 117 |

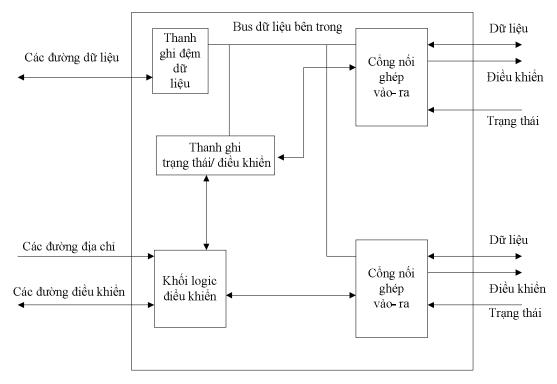

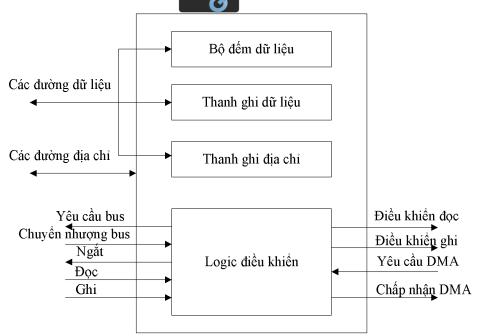

| 6.1.3. Mô-đun vào-ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

| 6.1.4. Địa chỉ hóa cổng vào ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 119 |

| 6.1.4.1. Không gian địa chỉ của bộ xử lý                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 119 |

| 6.1.4.2. Các phương pháp địa chỉ hóa cổng vào-ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 120 |

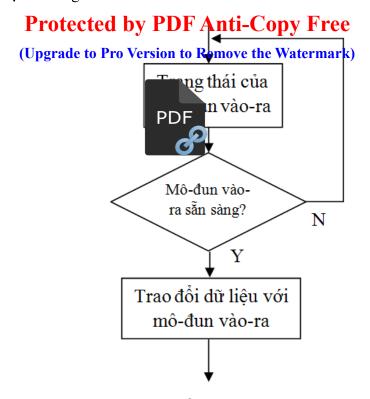

| 6.2. CÁC PHƯƠNG PHÁP TRAO ĐỔI DỮ LIỆU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| 6.2.1. Vào-ra bằng chương trình                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

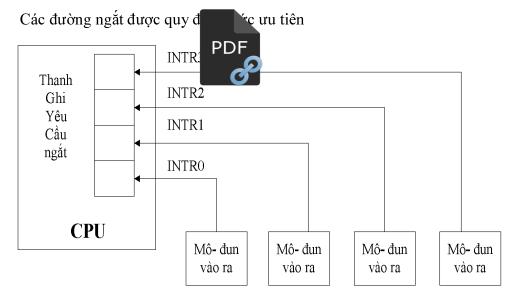

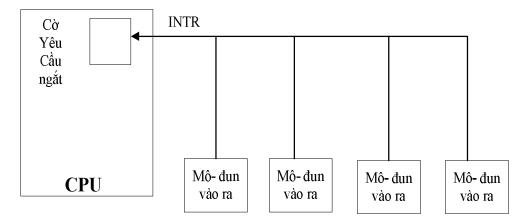

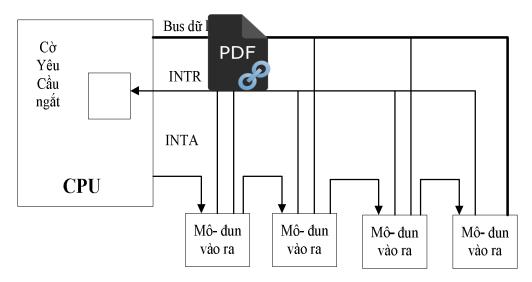

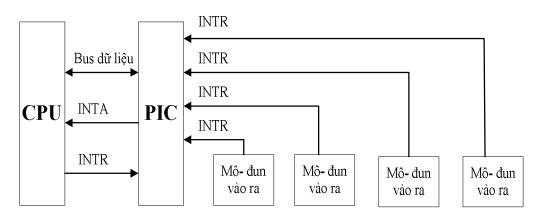

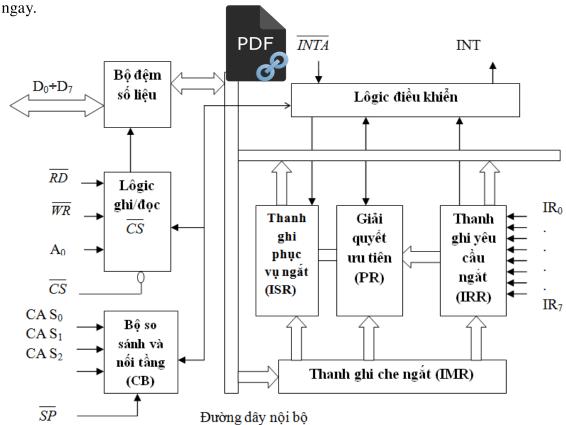

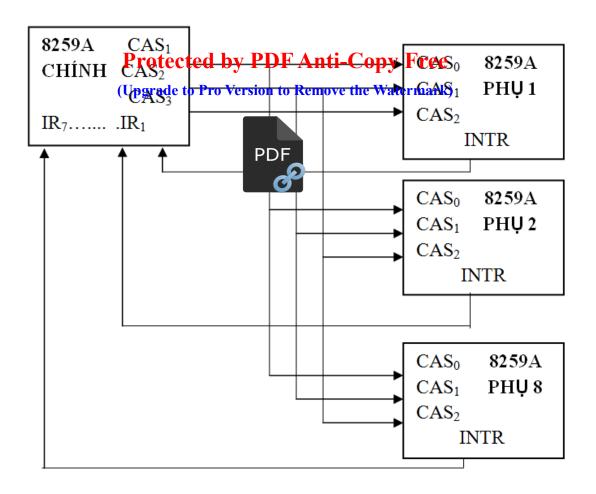

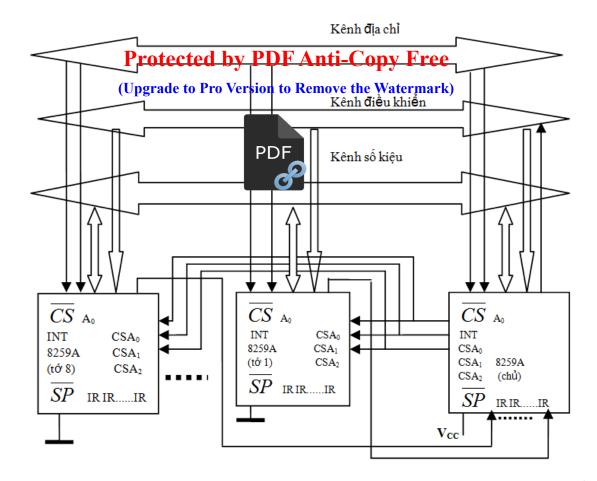

| 6.2.2. Vào-ra điều khiển bằng ngắt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 121 |

| 6.2.3. Truy nhập bộ nhớ trực tiếp – DMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125 |

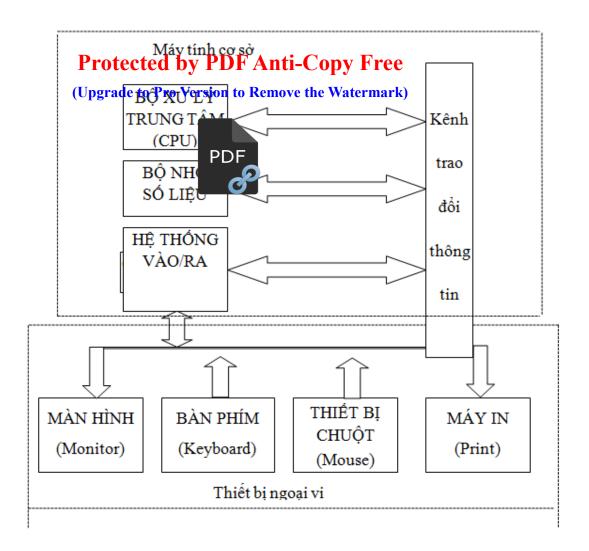

| 6.2.4. Kênh vào-ra hay bộ xử lý vào-ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 126 |

| 6.3. GHÉP NỐI VỚI THIẾT BỊ NGOẠI VI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 126 |

| 6.3.1. Các kiểu nối ghép vào ra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

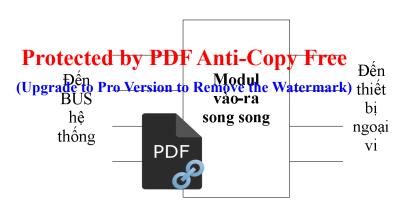

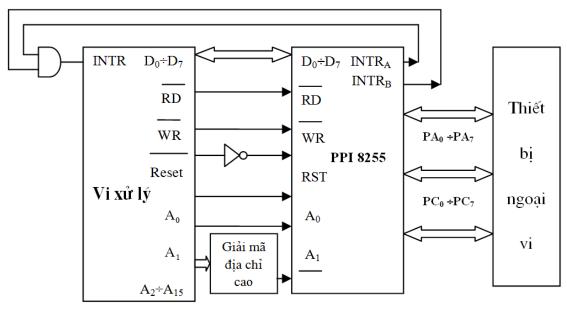

| 6.3.1.1. Nối ghép song song                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 126 |

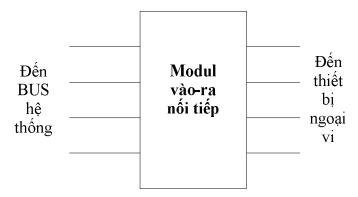

| 6.3.1.2. Nối ghép nối tiếp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

| 6.3.2. Các cấu hình ghép nổi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

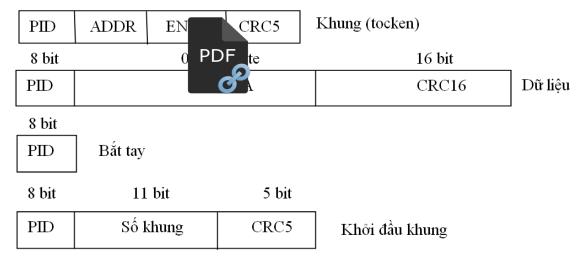

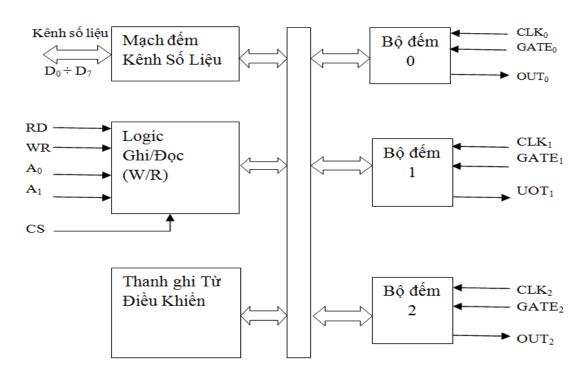

| Chương 7: GIAO DIỆN TRUYỀN DỮ LIỆU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 129 |

| 7.1. GIAO DIỆN SONG SONG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

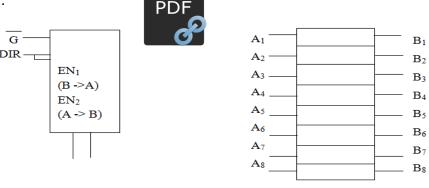

| 7.1.1. Mạch thu/phát đệm dữ liệu SN74LS245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

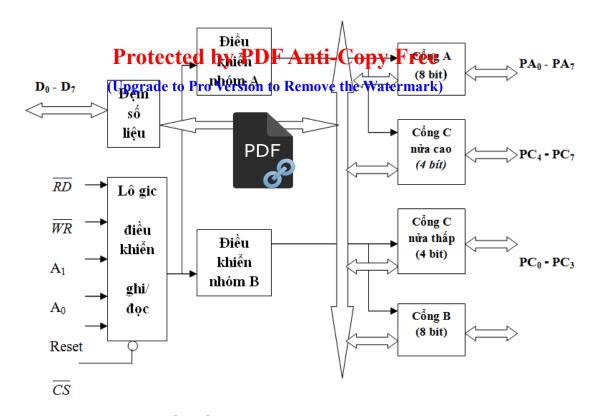

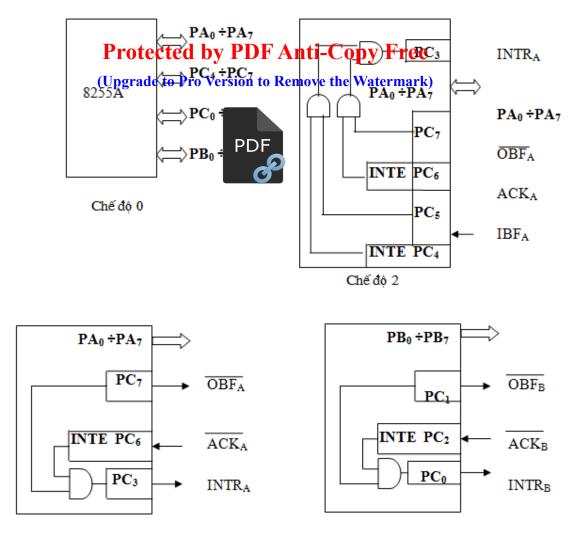

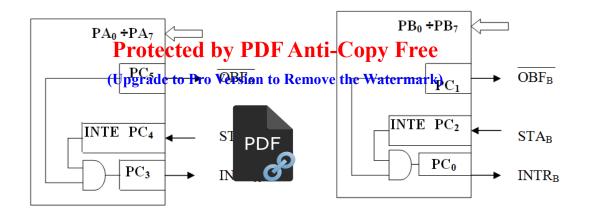

| 7.1.2. Mạch tương thích với ngoại vi chương trình hoá 8255A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 131 |

| 7.2. Giao diện tuần tự                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

| 7.3. Giao diện đa năng USB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 141 |

| 7.4. Giao diện cao tốc IEEE 1394                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     |

| TÀI LIÊU THAM KHẢO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

#### LỜI NÓI ĐẦU

Protected by PDF Anti-Copy Free Giáo trình Kiến trúc máy tính được biến soạn làm tài liệu giảng dạy của các Trường Đại học Công nghệ GTVT than yêu cầu, mục tiêu đào tạo của Nhà trường.

Giáo trình Kiến trúc máy cấp cho sinh viên các kiến thức cơ sở của PDF bô nhớ, bô nhớ trong, bô nhớ cache và các kiến trúc máy tính; hệ thống phân loai bô nhớ ngoài và các thiết bị oi dung của giáo trình được biên soan thành bảy chương:

Chương 1: Trình bày lịch sử phát triển của máy tính, cũng như các tính năng mới của máy tính trong từng giai đoạn; các thành phần cơ bản của máy tính.

Chương 2: Trình bày các phương pháp biến đổi cơ bản của hệ thống số; cách biểu diễn thông tin trong máy tính.

Chương 3: Giới thiêu cấu trúc của bô xử lý trung tâm: tổ chức, chức nặng và nguyên lý hoat động của các bộ phân bên trong bộ xử lý như bộ tính toán logic số học. bô điều khiển, tập các thanh ghi. Giới thiệu ngôn ngữ lập trình và chương trình dịch.

Chương 4: Giới thiêu bô điều khiển tao ra sư vân chuyển tín hiệu bên trong bô xử lý nhằm thực hiện tập lệnh tương ứng với kiến trúc phần mềm đã đề ra. Mô tả diễn tiến thi hành một lệnh mã máy, đây là cơ sở để hiểu được các hoạt động xử lý lệnh trong máy tính.

Chương 5: Chương này giới thiệu chức năng và nguyên lý hoạt động của các cấp bô nhớ máy tính: bô nhớ cache: nguyên lý vân hành, phân loại các mức, đánh giá hiệu quả hoat đông; và nguyên lý vân hành của bô nhớ ảo.

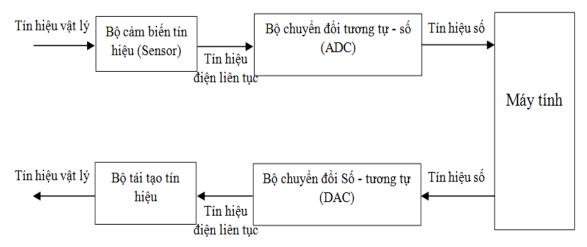

Chương 6: Hệ thống chuyển dữ liệu giữa máy tính và thiết bị ngoại vi, các phương pháp trao đổi dữ liệu và các cách ghép nối với thiết bi ngoại vi.

Chương 7: Giới thiệu chung về cấu trúc của hệ thống truyền dữ liệu, các phương pháp trao đổi dữ liệu song song, nối tiếp, giữa máy tính và thiết bị ngoại vi.

Giáo trình được biên soạn dựa trên kinh nghiệm giảng dạy môn học Kiến trúc máy tính tại Đại học Công nghệ GTVT của nhóm biên soạn. Tài liệu có thể được sử dụng làm tài liệu học tập, tham khảo cho sinh viên hệ đại học và cao đẳng ngành điện tử viễn thông và công nghệ thông tin.

Phân công biên soan giáo trình như sau: TS. Đỗ Quang Hưng biên soan lý thuyết và bài tập Chương 1 và Chương 2; KS. Phạm Trường Giang biên soạn lý thuyết và bài tập Chương 4, Chương 5 và Chương 6; ThS. Bùi Hải Đặng biên soan lý thuyết và bài tập Chương 3 và Chương 7. Giáo trình được biên soạn lần đầu nên khó tránh khỏi những thiếu sót. Nhóm biên soan rất mong nhân được các góp ý, cũng như ý kiến về việc cập nhật, hoàn thiên nôi dung của giáo trình.

> Nhóm biên soạn Hà Nội, tháng 2 năm 2017

### CÁC TỪ VIẾT TẮT

Protected by PDF Anti-Copy Free

Arithmetic and Logic Unit

(Upgrade to Pro Version to Remove the Watermark)

Binary Coded Decimal **ALU**

**BCD**

CD Con

Read Only Memory Con CD-ROM

CD CD-RW

Central Processing Unit **CPU**

**DMA Direct memory Access**

Dynamic RAM **DRAM**

DVD Digital Video Disk

FR Flag register

Institute of Electrical and Electronic Engineers **IEEE**

Least Significant Bit LSB

Most Significant Bit **MSB**

PIC Programmable Interrupt Controller

Redundant Array of Independent Disks **RAID**

**RAM** Random Access Memory

**ROM** Read Only Memory

**USB** Universal Serial Bus

#### Chuong 1

# GIÁTURACHY PO FÉAKIÉNCIBY CEMÁN TÍNH

Trang b**ị cha sinh tọi ền nha viện Rate với bản Wề triển với** máy tính: Các khái niệm, các thành phần cơ bản, phả triển của máy tính và lịch sử phát triển của máy tính.

### 1.1. CÁC KHÁI NIỆM VÀ NGƯ TENEY CƠ BẢN

#### 1.1.1. Mở đầu

Kiến trúc máy tính là khoa học về việc lựa chọn và kết nối các thành phần phần cứng để tạo ra các máy tính đạt được các yêu cầu về chức năng (functionality), hiệu năng (performance) và giá thành (cost). Yêu cầu chức năng đòi hỏi máy tính phải có thêm nhiều tính năng phong phú và hữu ích; yêu cầu hiệu năng đòi hỏi máy tính phải đạt tốc độ xử lý cao hơn và yêu cầu giá thành đòi hỏi máy tính phải càng ngày càng rẻ hơn. Để đạt được cả ba yêu cầu về chức năng, hiệu năng và giá thành là rất khó khăn. Tuy nhiên, nhờ có sự phát triển rất mạnh mẽ của công nghệ vi xử lý, các máy tính ngày nay có tính năng phong phú, nhanh hơn và rẻ hơn so với máy tính các thế hệ trước.

#### 1.1.2. Khái niệm máy tính

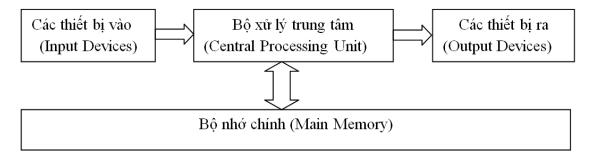

Máy tính (computer) là một thiết bị điện tử hoạt động dưới sự điều khiển của các chỉ thị được lưu trữ trong bộ nhớ. Nó thực hiện các công việc sau:

- Nhận thông tin đầu vào

- Xử lý thông tin theo chương trình được lưu trong bộ nhớ

- Đưa thông tin ra

Máy tính hoạt động theo chương trình.

Hình 1.1. Mô hình máy tính cơ bản

#### 1.1.3. Kiến trúc máy tính và cấu trúc máy tính

- Kiến trực máy tính (architecture) nghiện cứu những thuộc tính của một hệ thống mà người lập trình có thể nhìn thấy được, những thuộc tính quyết định trực tiếp đến việc thực thi một chương trình toán, xử lý dữ liệu

- Cấu trúc máy tính (struct phiên cứu về các thành phần chức năng và sự kết nối giữa chúng để tạo nên một thuật của kiến trúc.

Những thuộc tính liên quan đến kiến trúc bao gồm tập lệnh cơ bản mà CPU có thể thực hiện, số bit được sử dụng để biểu diễn các loại dữ liệu khác nhau, cơ chế nhập/xuất dữ liệu và các kỹ thuật đánh địa chỉ ô nhớ,...Cấu trúc máy tính lại bao gồm các thuộc tính kỹ thuật mà người lập trình không nhận biết được như các tín hiệu điều khiển, giao diện giữa máy tính và thiết bị ngoại vi, công nghệ xây dựng bộ nhớ...